# 4-BIT MICROCOMPUTERS for DIGITAL TUNING SYSTEMS (CMOS)

#### MB88560 SERIES

April 1987 Edition 2.0

#### DESCRIPTION

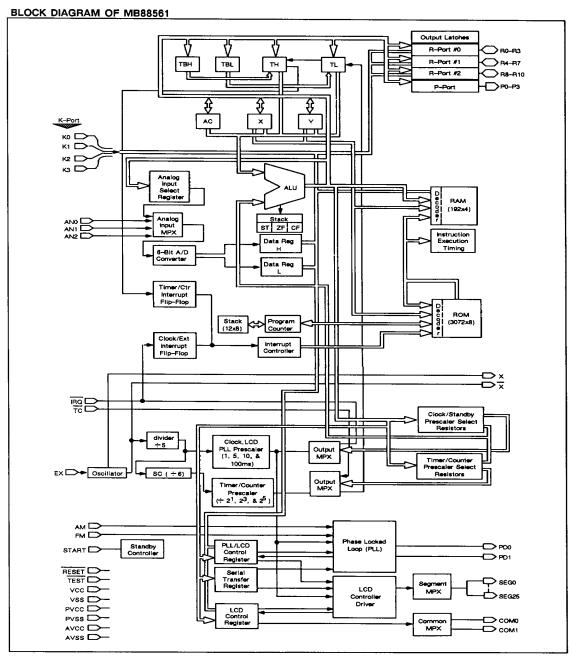

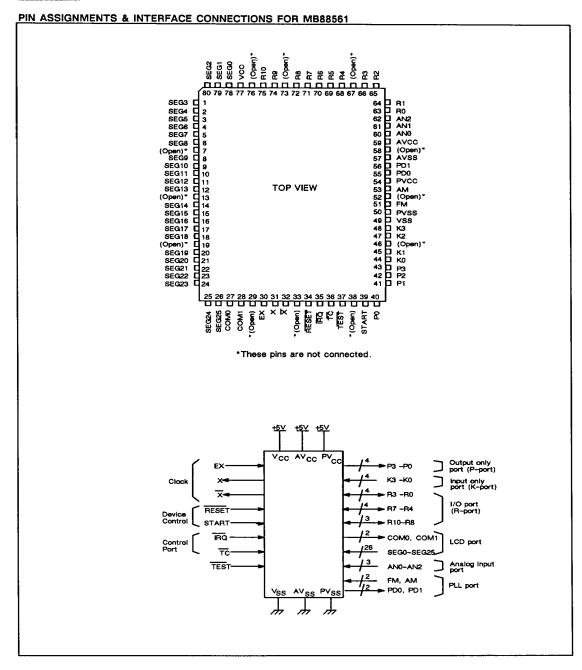

The Fujitsu MB88560 series is an upgraded version of the MB88500 family and consists of two 4-bit microcomputers-the MB88561 with an LCD display controller/driver and the MB88562 with a VFD display driver. The architecture of each device (MB88561 and MB88562) is similar to counterpart products in the MB88500 series; however, to improve both flexibility and efficiency, an A/D converter, a phase locked loop (PLL), and on-chip display drivers are added. When high quality and low cost are primary design considerations, the MB88561 and/or the MB88562 is an excellent choice for digital tuning systems such as those used in automobile radios, stereo tuners, and other similar applications.

The MB88561 LCD device contains a 3K by 8-bit mask ROM (program memory) and a 192 by 4-bit static RAM (data memory) whereas, the MB88562 VFD device contains a 4K by 8-bit mask ROM and a 256 by 4-bit static RAM. Besides the on-chip memory, each device has 21 I/O lines, an 8-bit timer/counter, an A/D converter with 6-bit resolution, display drivers, and a phase locked loop (PLL) that is suitable for all broadcast and shortwave frequencies. Each device has independent AM (up to 32 MHz) and FM (up to 120 MHz) inputs.

Controller/driver circuits of the MB88561 can directly drive 1/2 duty, 1/2 bias, 20-millisecond frame-cycle LCD devices: 52-segment LCD displays are available. VFD driver ports of the MB88562 are N-channel middle-voltage outputs with pull-down resistors; with a 12-volt power supply, these outputs can directly drive 39-segment VFD devices.

Mask options for the MB88560 series are shown in the following table. These options must be specified by the Customer when a device is ordered; data release forms for specifying the options are available at Fujitsu Sales Offices.

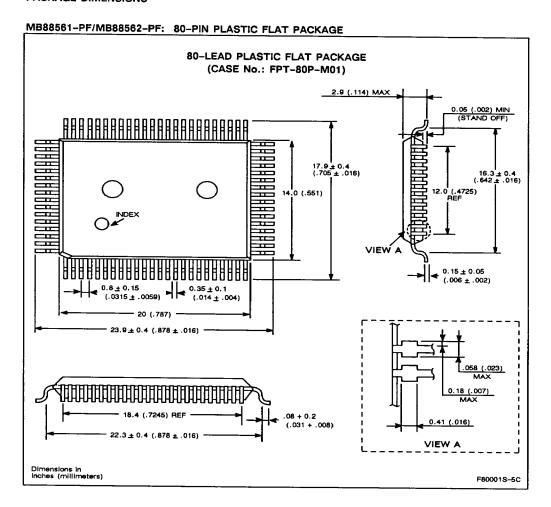

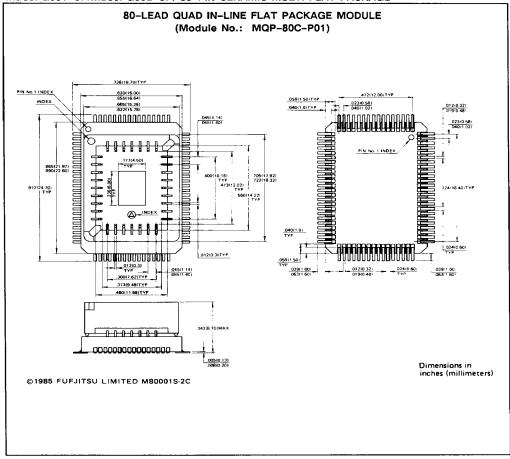

Both devices are fabricated in silicon-gate CMOS and are housed in an 80-pin plastic flat package. The MB88561 and MB88562 require a +5V power supply and operate over a temperature range of -40°C to +85°C.

To minimize system cost and development time, Fujitsu provides a complete complement of hardware and software development tools- refer to "Table 1. Specification Summary and Development Tools."

This device contains circuitry to protect the inputs against darnage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### **USER MASK OPTIONS**

| Function                         | Option                                 | Remarks                                                                    | Function                                      | Option      | Remarks                 |

|----------------------------------|----------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------|-------------|-------------------------|

| Output port type                 | Standard open-drain<br>Standard pullup | Selected output port option must be the same for all P- and R-ports        | Standby off reset                             | No<br>Yes   |                         |

| Standby                          | No<br>Yes (software<br>initiated)      |                                                                            | Output port level during reset                | High<br>Low | R10 to R8<br>fixed high |

| Output port state during standby | Hold<br>High-Z                         | Selected port-state<br>option must be the<br>same for all P-and<br>R-ports | Pull-down resistor for<br>segment output port | No<br>Yes   | MB88562<br>Only         |

#### **FEATURES**

Program Memory

MB88561: 3K x 8-bit mask ROM

MB88562: 4K x 8-bit mask ROM

Data Memory

MB88561: 192 x 4-bit static RAM

MB88562: 256 x 4-bit static RAM

21 I/O Ports

O P-port: 4-bit parallel output only

K-port: 4-bit parallel input only

R-port: Two 4-bit and one 3-bit parallel

R-port: Two 4-bit and one 3-bit parallel input/output or 11 individual input/output lines

C-port: External interrupt input; timer/ counter input

Two Selectable Output Port Circuits (P and R Ports—Mask Options):

o Standard open drain

O Standard pullup

8-Bit Programmable Timer/Counter with Auto-Load Function and Two Clock Modes:

o Internal clock (timer)

External clock (counter)

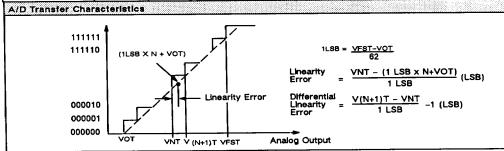

6-Bit Programmable A/D Converter with 3 Multiplexed Analog inputs and Sample/Hold Circuits (Successive Approximation Type Converter)

On-Chip Phase Locked Loop (PLL) for Digital Tuning Systems;

o 15-bit prescaler

o 4.5 MHz reference frequency

Independent AM and FM input terminals

Two phase detector outputs

• Single Level Three Source Maskable Interrupt:

External

o Clack

Timer/counter overflow

Instruction Set (Upward compatible with MB88500 Series):

Number of Instructions: 70 for MB88561; 7I for MB88562

Instruction byte length/cycle count: 1/1, 2/2, and 2/3

Execution time: 6.67 μs (min) using 4.5 MHz clock

• Four Nesting Levels for Subroutine Calls

· Software initiation of Low-Power Standby

Selectable Output Port States During Standby (Mask Option): o Hold

High impedance

· Oscillator Programmable States During Standby:

o idle

Stop

Other Mask Options:

Standby off reset

On-Chip Power-On Reset

On-Chip Clock Generator and I/2 Clock Prescaler

MB88561—On-Chip Liquid Crystal Display (LCD) Controller/Driver:

o Direct drive for LCD.

Two common outputs and 26 segment outputs.

13 x 4-bit display memory independent of data memory space.

Segment data table can be stored in program memory (mask ROM).

1/2 duty and 1/2 bias (on-chip LCD bias circuits).

MB88562—On-chip Vacuum Fluorescent Display (VFD) Driver:

Direct drive for 39-segment VFD (+12Vdc).

N-channel middle-voltage outputs with pull-down resistors.

Low Power Dissipation:

MB88561 (Active Mode) —27.5 mA (max) with following conditions:

fc = 4.5 MHz

VCC = AVCC = PVCC = 5.5V

MB88561 (Standby Mode)—30 μA (max)

fc = 0 MHz

VCC = AVCC = PVCC = 6.0V

MB88562 (Active Mode) — 42.5 mA (max) with following conditions:

f<sub>C</sub> = 4.5 MHz

VCC = PVCC = 5.5V; SEGVCC = 12.5V

MB88562 (Standby Mode) —20 μA (max) with

f<sub>C</sub> = 0 MHz VCC = PVCC = 6.0V

• Powerful Development Support (refer to Table 1)

Wide Range of Operating Temperatures:

T<sub>A</sub> = -40°C to +85°C.

• 80-Pin Plastic Flat Package: FPT-80P-M01

Table 1. Specification Summary and List of Development Tools

| Tubic ii opcomoznem cum                           | mary and List of Development Tools  MB88561-PF                         | MB88562-PF                                                                                        |  |  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| ROM size                                          | 3K x 8 bits                                                            | 4K x 8 bits                                                                                       |  |  |  |  |

| RAM size                                          | (On-chip mask ROM)                                                     | (On-chip mask ROM)                                                                                |  |  |  |  |

| (Directly addressed locations)                    | 192 x 4 bits (Addresses 0-7)                                           | 256 x 4 bits (Addresses 0-7)                                                                      |  |  |  |  |

| I/O port:                                         | Total 21 lines                                                         | Total 21 lines                                                                                    |  |  |  |  |

| Input-only port<br>Output-only port               | 4                                                                      | 4                                                                                                 |  |  |  |  |

| I/O port<br>Control port                          | 11                                                                     | 11 2                                                                                              |  |  |  |  |

| Output port type                                  | Standard pull-up<br>Standard open-drain (Mask option)                  | Standard pull-up<br>Standard open-drain (Mask option)                                             |  |  |  |  |

| Stack depth (Nesting level)                       | 4 levels                                                               | 4 levels                                                                                          |  |  |  |  |

| Timer/Counter:<br>Buffer size<br>Clock source     | Yes (Auto Load function)<br>8 bits<br>internal/External                | Yes (Auto Load function)<br>8 bits<br>internal/External                                           |  |  |  |  |

| Serial I/O                                        | No                                                                     | No                                                                                                |  |  |  |  |

| Clock generator:                                  | Yes                                                                    | Yes                                                                                               |  |  |  |  |

| Oscillator type<br>Clock frequency                | Crystal/External<br>4.5MHz                                             | Crystal/External<br>4.5MHz                                                                        |  |  |  |  |

| Interrupt function:                               | Yes                                                                    | Yes                                                                                               |  |  |  |  |

| Nesting level                                     | Single level                                                           | Single level                                                                                      |  |  |  |  |

| Interrupt sources                                 | 3 sources                                                              | 3 sources                                                                                         |  |  |  |  |

| Standby function:                                 | Yes/No (Mask option)                                                   | Yes/No (Mask option)                                                                              |  |  |  |  |

| Initiation method Oscillator state during standby | Software Idle or stop (Software selectable)                            | Software Idle or stop (Software selectable)                                                       |  |  |  |  |

| Output state during standby                       | Hold or High- Z (Mask option)                                          | Hold or High- Z (Mask option)                                                                     |  |  |  |  |

| Standby off reset function                        | Yes/No (Mask option)                                                   | Yes/No (Mask option)                                                                              |  |  |  |  |

| Watch dog timer function                          | No (Fixed)                                                             | No (Fixed)                                                                                        |  |  |  |  |

| Number of Instructions                            | 70                                                                     | 71                                                                                                |  |  |  |  |

| Instruction byte length/<br>cycle count           | 1/1, 2/2, or 2/3                                                       | 1/1, 2/2, or 2/3                                                                                  |  |  |  |  |

| Instruction execution time                        | 6.67 µs (min) at 4.5 MHz                                               | 6.67 μs (min) at 4.5 MHz                                                                          |  |  |  |  |

|                                                   | (With prescaler)                                                       | (With prescaler)                                                                                  |  |  |  |  |

| Power supplies:                                   |                                                                        | 4.5V to 5.5V (VCC=AVCC);                                                                          |  |  |  |  |

| Active                                            | 4.5V to 5.5V (VCC=PVCC=AVCC)                                           | 11.5V to 12.5V (SEGVCC)                                                                           |  |  |  |  |

| Standby                                           | 3.5V to 6.0V (VCC=PVCC=AVCC)                                           | 3.5V to 6.0V (VCC=AVCC)                                                                           |  |  |  |  |

| Operating temperature range                       | -40°C to +85°C                                                         | -40°C to +85°C                                                                                    |  |  |  |  |

| Process                                           | CMOS                                                                   | смоѕ                                                                                              |  |  |  |  |

| Package                                           | 80-pin FPT                                                             | 80-pin FPT                                                                                        |  |  |  |  |

| Development tools:                                | MB2115-01 : CRT unit (MB8856                                           | 1 and MD99562)                                                                                    |  |  |  |  |

| Hardware                                          | MB2115-02 : Monitor board with                                         | n keyboard (MB88561 and MB88562)                                                                  |  |  |  |  |

|                                                   | MB88562                                                                | 232Ć Interface unit (MB88561 and                                                                  |  |  |  |  |

|                                                   | MB2115-40 : DUE board (for M<br>MB2115-41 : DUE board (for M           | B88561)<br>B88562)                                                                                |  |  |  |  |

| Software                                          | MB88PG561-CF : Piggyback evaluat                                       | on device (for MB88561)                                                                           |  |  |  |  |

|                                                   | M888PG562-CF : Piggyback evaluat SM05215-A010 : Intellec series II/III | valuation device (for MB88561)<br>valuation device (for MB88562)<br>es II/III MDS cross-assembler |  |  |  |  |

|                                                   | SM07415-A012 : CP/M-86 cross-a                                         | ssembler                                                                                          |  |  |  |  |

|                                                   | SM07615-AXXX : PC-DOS cross-as<br>SM07415-G022 : CP/M-86 host em       | sembler<br>ulator                                                                                 |  |  |  |  |

| 1                                                 | SM07615-GXXX : PC-DOS host em                                          | ulator                                                                                            |  |  |  |  |

**BLOCK DIAGRAM OF MB88562** Output Latches R-Port #0 O R0-R3 R-Port #1 O 84-87 TBL TH TL P-Port - P0-₽3 ₹ K-Port Y ко 🗅 к1 🗅 K2 □ кз 🗁 Analog Input Select Registe RAM Analog Stack ST ZF CF Input MPX Instruction Data Reg Execution Timing н 6-Bit A/D Data Reg Timer/Ctr interrupt Stack (12x8) Program Counter Clock/Ext Controller R B Clock/Standby Prescaler Sele Resistors Divider Ш ÷ 5 PLL Prescaler (1, 5, 10, & Timer/Counter 100ms) Ex Oscillator SC (+6) Resistors Timer/Counter Prescaler -1- 2, 2, 8.2,5 SEGG Segment Drivers AM D Standby Controller PLL/LCD Control START [ Register -D P00 RESET -Loop (PLL) -D PD1 TEST 🗅 Transfer vcc 🖵 vss 🗁 PVCC 🗁 A/D Control Register PVSS 🗁 SEGVCC -

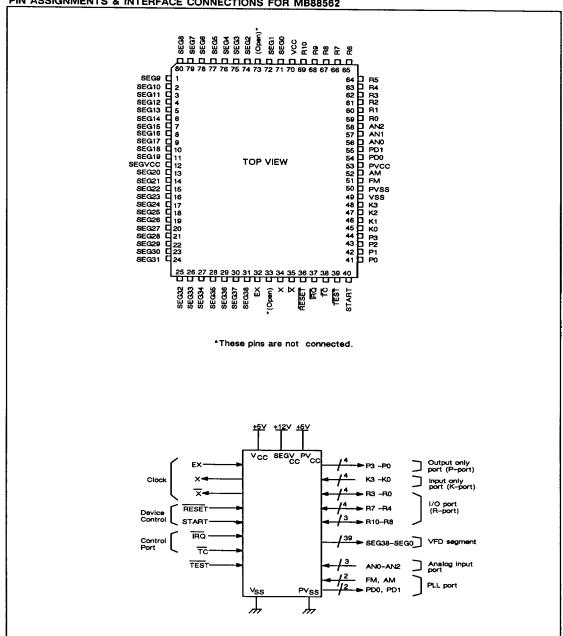

## PIN ASSIGNMENTS & INTERFACE CONNECTIONS FOR MB88562

## FUJITSU MB88560 SERIES

PIN DESCRIPTIONS

|                | SCRIPT         | ONS              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                | No.<br>MB88562 | Designator       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin<br>MB88561 | No.<br>MB88562 | Designator | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 77<br>49<br>30 | 70<br>49<br>32 | VCC<br>VSS<br>EX | +5V DC power supply. Ground. Input to on-ohip oscillator. A 4.5 MHz crystal is externally connected between the EX and X pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                |            | The logical state of the START pin can be sensed by executing an IN instruction (Y=8) to read the standby status register. The logic level is indicated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 31             | 34             | ×                | Output of on-chip oscilla-<br>tor; input for the internal<br>clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                |            | by the standby release in-<br>put flag (STIF). The<br>START pin is a hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 32             | 35             | ≖                | Provides an inverted clock output for external sync functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35             | 37             | ĪRQ:       | input with an internal 300k-<br>ohm pullup resistor.<br>Maskable external interrupt<br>input to the on-chip inter-<br>rupt control circuit. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 34             | 36             | RESET            | An external reset input and a power-on reset output. When set to a LOW logic level, halts operation of the MCU and initializes the device. When the RESET pin returns to a HiGH logic level, program execution restarts at address 0. When the oscillator stabilizes after power-on, the RESET pulse must be LOW for at least two instruction cycles to properly initialize the device. To implement an external reset, connect a capacitor between the RESET pin (Internal pull-up resistor) and ground (VSS pin); the time constant should be greater than the time interval of 12 clock                                                                                                                                                                                                                                      |                |                |            | rupt control circuit. The falling edge of IRQ sets the external interrupt request flag (IRF) in the interrupt flag register regardless of whether the external interrupt is enabled or disabled. If the external interrupt is enabled on advance by an EN instruction, the interrupt is immediately serviced; if not enabled, the IRF flag is internally held as an interrupt source.  The logic level of the IRQ pin can be tested with a TSTI instruction; when IRQ is LOW, the interrupt flag (IF) is HIGH. For all other conditions, IF is LOW. The IRQ pin is a hysteresis input with an internal 300k-ohm pullup resistor.                                                                                                                                                                                                  |  |  |  |

| 39             | 40             | START            | periods. When the device is powered up, the on-chip reset control circuit outputs a Low level on this pin. Except for the reset mode, the output is High during normal operation. The rise of VCC (50µs to 50ms of rise time) causes a Low output from the RESET pin; it automatically returns to a High state approximately 80-milliseconds after the on-chip oscillator starts. The RESET pin is a hysteresis input with an internal 300k-ohm pullup resistor.  Release input for the standby control fatatus registers; these registers monitor and control the on-chip standby control circuits. During the standby mode, a HIGH level on the START pin sets the standby release flag (STF) in the standby status register, resets the standby enable flag (STBE) in the standby enable flag (STBE) in the standby control. | 36             | 38             | TC         | Clock-count input pulses to the on-chip 8-bit timer/ counter. The falling edge of TC increments the timer/counter by one count under the following cond-litions:  • When external count clock (counter) mode is selected by EN instruction.  • When timer/counter prescaler select register is programmed to enable the TC input using OUT instruction (Y=B).  OUT instruction (Y=B).  OUT instruction (Y=B).  The TC pin is inactive as a clock-count input when the external clock-count mode is disabled by RESET or by a DIS instruction, or the TC input is not selected by the timer/counter prescaler select register.  The logic level of the TC pin is always indicated by the timer/counter input flag (TCIF) in the timer/counter (TCIF) in the timer/counter (TCIF) in the timer/counter (TCIF) in the timer/counter. |  |  |  |

|                |                |                  | In the standby control register and triggers the sequence that returns the MCU to an active mode. Before the START pulse is applied, VCC must return to the normal operating range (+5V ± 10%) when a backup battery is used. Also, the START pin must be LOW before initiating the standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                |            | er prescaler select register. The logic level of the TC pin can be tested by using an IN instruction (Y=B) to read the prescaler select register; when TC is LOW, the TCIF flag is HIGH. For all other conditions, TCIF is LOW. The TC pin is a hysteresis input with an internal 300k-ohm pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

PIN DESCRIPTIONS (Cont'd)

| Pin N                          |                         | ONS (Co                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin N                                              | do.                           |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|-------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MB88561                        | MB88562                 | Designator               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MB88561                                            | MB88562                       | Designator               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 48-47,<br>45-44<br>43-40       | 48-47,<br>46-45         | K3-K0                    | K-port. A 4-bit parallel non-<br>latched input-only port; K0<br>is LSB. K-port data is input<br>to accumulator via an INK<br>instruction. All K-port pins<br>have internal pullup resist-<br>ors.  P-port. A 4-bit parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7, 13,<br>19, 29,<br>33, 38,<br>46, 52,<br>58, 67, | 33, 73                        | Open                     | No connection to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                |                         |                          | latched output-only port;<br>P0 is LSB. Data from the<br>accumulator is output to<br>the P-port via an OUTP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73, 76<br>59                                       |                               | AVCC                     | +5V DC power supply voltage for A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |                         | _                        | instruction. Refer to<br>DESCRIPTION for available<br>masking options.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57                                                 |                               | AVSS                     | Ground pin for A/D convert-<br>er.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 66-63<br>71-68<br>75-74,<br>72 | 62-59<br>66-63<br>69-67 | R3-R0<br>R7-R4<br>R10-R8 | The R-port serves as two 4-bit and one 3-bit parallel non-latched inputs/latched outputs or 11 individual non-latched inputs/latched outputs ines. The selected service depends on the sequence of instructions. Using the parallel I/O structure, the two 4-bit ports are designated R-port #0 (R3-R0) and R-port #1 (R7-R4); the 3- bit port is designated R- port #2 (R10-R8). All three ports are indirectly addressable by port num- ber via the Y-register. Four-bit (or three-bit) data from the accumulator is output to the addressed R-port via an OUT instruction; four-bit (or three-bit) data from one port is input to the accumulator via an IN instruction. Before exe- cuting an IN instruction, the addressed port must be set to a High (input) mode), logic level. | 54<br>50<br>51<br>53                               | 58-56<br>53<br>50<br>51<br>52 | PVCC<br>PVSS<br>FM<br>AM | of three analog input ports is selected via the analog input select register (Y = D). The A/D converter is activated by writing a "1" to bit #0 of the A/D control register (Y = 9). When conversion is complete, the high-order bits are placed in the A/D data register (Y=F) and the low-order two bits are put into the A/D data register (Y=F).  +5VDC power supply voltage for PLL.  Ground pin for PLL.  Local oscillator inputs. The PLL consists of a reference clock generator prescaler, a local oscillator input and a comparator. The reference clock frequency can be selected from anyone of the following: 25 kHz, 12.5 kHz, 10 kHz, 9 kHz, 5kHz, or 1.0 kHz.  Local oscillator input for FM. The local oscillator input for FM. |

|                                |                         |                          | mode) logic level. When the R-port lines are used individually, each line (R10-R0) can be indirectly addressed by bit number via the Y-register Each addressed bit line can be set or reset by a SETR/RSTR instruction; the lines of R-port #0 (R3-R0) can be directly set or reset by a SETD/RSTD instruction. Each addressed line is individually testable by a TSTR instruction; each line of R-port #2 can be directly tested with a TSTD instruction. Before executing a TSTD or TSTR                                                                                                                                                                                                                                                                                             | 55–56                                              | 54-55                         | PD0, PD1                 | grammable prescaler has a 15-bit pulse swallow divider. The FM local frequency is input to the FM terminal.  Local oscillator input for AM. A 15-bit pulse swallow divider and also a direct divider are provided for the local oscillator programmable prescaler; the prescaler can be selected by software The AM local frequency is input to the AM terminal.  Phase comparison error outputs. Signals from the local oscillator input and the reference clock are                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 37                             | 39                      | TEST                     | instruction, the addressed bit line must be set to a High (Input mode) logic level. Refer to description for available mask options. Used to activate the test mode for the purpose of shipping tests at Fujitsu. This pin is normally set to a High logic level with an internal pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27,28                                              |                               | COM0,<br>COM1            | compared: the error signal is output on PD0/PD1.  Common outputs for Liquid Crystal Display (LCD). Two one-half duty cycle, one-half blas LCD drivers are used for common outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### PIN DESCRIPTIONS (Cont'd)

|                                            |                                              | 10110 (001                                  |                                                                                                                                                                                                                                     |         |                                                   |                                                                            |                                                                                                                                                                                                                                                                                     |  |  |

|--------------------------------------------|----------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pit                                        | n No.                                        |                                             | F                                                                                                                                                                                                                                   | Pin     | No.                                               | Designator                                                                 | Function                                                                                                                                                                                                                                                                            |  |  |

| MB88561                                    | MB88562                                      | Designator                                  | Function                                                                                                                                                                                                                            | MB88561 | MB88562                                           | Designator                                                                 | FullCtion                                                                                                                                                                                                                                                                           |  |  |

| 26-20,<br>18-14,<br>12-8,<br>6-1,<br>80-78 |                                              | SEG25-<br>SEG0                              | Segment outputs for LCD. Twenty six one-half duty cycle, one-half blas LCD drivers are used for segment outputs. In addition to internal RAM, an on-chip segment data memory of 13 x 4 bits is available to store the display data. |         | 11-8<br>16-13<br>20-17<br>24-21<br>28-25<br>31-29 | SEG 19-16<br>SEG 23-20<br>SEG 27-24<br>SEG 31-28<br>SEG 35-32<br>SEG 39-36 | The 4-bit ports are con-<br>secutively designated SEG<br>port #0 (SEG 3-0) through<br>SEG port #8 (SEG 35-32);<br>the 3-bit port is designated<br>as SEG port #9 (SEG<br>39-36). The ports are in-<br>directly addressable by<br>port number via the Y-reg-<br>ister. Data from the |  |  |

|                                            | 12                                           | SEGVCC                                      | 12V DC power supply for VFD driver segment output.                                                                                                                                                                                  |         |                                                   |                                                                            | accumulator is output to an<br>addressed port (SEG port<br>#0 through SEG port #9)                                                                                                                                                                                                  |  |  |

|                                            | 75, 74,<br>72, 71<br>79-76<br>3-1, 80<br>7-4 | SEG 3-0<br>SEG 7-4<br>SEG 11-8<br>SEG 15-12 | Segment port. These lines serve as nine 4-bit and one 3-bit parallel latched output-only ports for VFD segments.                                                                                                                    |         |                                                   |                                                                            | by an OUTX instruction. The SEG ports are middle- voltage outputs with pull- down resistors and are driven Low by a RESET pulse.                                                                                                                                                    |  |  |

#### **OPERATIONAL GUIDELINES**

To achieve optimum performance and to minimize the chances of device failure, the MB88561 and/or the MB88562 should be used within the operating boundaries described in subsequent paragraphs.

#### **Device Latchup**

If latchup occurs, the supply current may increase to the point of thermal destruction. To prevent latchup, the operational limits and procedures specified below should be followed.

- Never apply a voltage higher than VCC or lower than VSS to any input or output pin.

- Voltages exceeding Absolute Maximum Ratings should not be applied between VCC and VSS pins—Refer to ELECTRICAL CHARACTERIS-TICS.

- Do not power-up MCU power supply (VCC) until power has been applied and is stabilized for the analog power supply (AVCC), PLL power supply (PVCC), and the VFD power supply (SEGVCC).

#### **Supply Voltages**

Abrupt changes in the operating supply voltages can cause device malfunction; therefore, well-regulated power supplies should be used. The ripple and rate-change values should not exceed the following:

- The peak-to-peak VCC ripple at commercial frequencies of 50-60 Hz should be less than 10% of the typical value of VCC.

- The transient change rate of VCC should be less than 0.1V/ms.

#### **Unused Input Pins**

Unused input pins should be pulled up-or-down with external resistors; However, the X pin should be open when an external clock is used.

#### TEST Pin

This input pin is used to activate the test mode for shipping test purposes at Fujitsu. When the TEST pin is forced to a low logic level while the RESET pin is low, the device enters the test mode. To prevent undesired activation of the test mode during normal operation, an external pull-up resistor is recommended in addition to the internal 10k-ohm pullup.

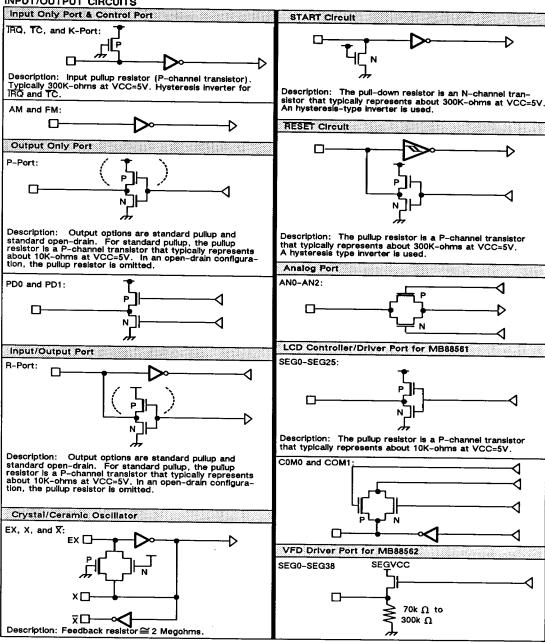

#### INPUT/OUTPUT CIRCUITS

2-617

#### **INSTRUCTION SET**

The Instruction set for the MB88560 microcomputer series consists of 70 instructions for the MB88561 and 71 instructions for the MB88562. Of the total, 84% are single-byte/single-cycle instructions, 15% are two-byte/single cycle instructions, 15% are two-byte/two-cycle instructions and 1% are two-byte/three-cycle instructions. The instruction set for the MB88560 series

is upward compatible with that of the MB88500 series and, as shown in Table 3, is divided into ten functional groups. Symbols and abbreviations that are commonly used in the instruction set are shown Table 2. Table 3 provides a summary of operational data and all instruction codes are summarized in Table 4.

Table 2. Symbols and Abbreviations Used In Instruction Set

| Symbols        | Meaning                                   | Abbreviation | Meaning                                                                               |  |  |  |  |  |  |

|----------------|-------------------------------------------|--------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

| +              | Is transferred to                         | AC           | Accumulator                                                                           |  |  |  |  |  |  |

|                |                                           | addr         | Jump address                                                                          |  |  |  |  |  |  |

| <del>-4-</del> | Is exchanged with                         | bp           | Bit pointer (that is part of the instruction code)                                    |  |  |  |  |  |  |

| +              | Arithmetic plus                           | C<br>CF      | Carry Carry flag                                                                      |  |  |  |  |  |  |

| -              | Arithmetic minus                          | d            | Direct line number (that is part of the instruction code)                             |  |  |  |  |  |  |

| Φ              | Logical EXCLUSIVE OR                      | IF.          | Interrupt flag                                                                        |  |  |  |  |  |  |

| n              | Logical OR                                | imm          | Immediate data                                                                        |  |  |  |  |  |  |

| υ              | Logical AND                               | ĪRQ          | interrupt request                                                                     |  |  |  |  |  |  |

| (overline)     | Negation                                  | К            | K-Port (K3 to K0)                                                                     |  |  |  |  |  |  |

| ( )            |                                           | LSB          | Least significant bit                                                                 |  |  |  |  |  |  |

|                | Contents of parenthesis                   | M(X,Y)       | Data memory (RAM) location indirectly                                                 |  |  |  |  |  |  |

| †              | Set to "1" always                         | M(0.D)       | addressed by data pointer (X- and Y- registers  Data memory (RAM) location directly   |  |  |  |  |  |  |

| Ţ              | Set to "0" always                         | M(0,D)       | addressed by "D" bits in the instruction code in page #0 (X=0)                        |  |  |  |  |  |  |

| 1              | Affected (set or reset)                   | MSB          | Most significant bit                                                                  |  |  |  |  |  |  |

|                | by operation results                      | Р            | P-Port (P3 to P0)                                                                     |  |  |  |  |  |  |

| †c             | Set to "0" due to carry (not carry flag)  | R            | R-Port (#0: R3-R0, #1: R7-R4, #2: R10-R8)                                             |  |  |  |  |  |  |

| ↓ IF           | Set to "0" due to interrupt flag          | (R)Y; Y=n    | 1 R-Port #n specified by Y-register (Y=0 to 3) 2 R-Port bit n specified by Y-register |  |  |  |  |  |  |

| ↓ CF           | Set to "0" due to carry flag              | (R)d; d=n    | (Y=0 to 10)  R-Port bit n specified by "d" bits in                                    |  |  |  |  |  |  |

| 1 VF           | Set to "0" due to                         |              | the instruction code                                                                  |  |  |  |  |  |  |

| + **           | timer/counter overflow flag               | SEG          | Segment port (#0: SEG3-SEG0,#7: SEG39-SEG36) :MB88562                                 |  |  |  |  |  |  |

| ţΖ             | Set to "0" due to<br>zero (not zero flag) | ST           | Status flag                                                                           |  |  |  |  |  |  |

| ↓ ZF           | Set to "0" due to zero flag               | TH<br>TL_    | Timer/counter high byte Timer/counter low byte                                        |  |  |  |  |  |  |

| -              |                                           | VF           | Timer/counter overflow flag                                                           |  |  |  |  |  |  |

|                | Not affected                              | Х            | X-register (that indicates page # in data memory RAM)                                 |  |  |  |  |  |  |

|                | 1                                         | Xn           | The n-th bit X-register                                                               |  |  |  |  |  |  |

|                |                                           | Υ            | Y-register                                                                            |  |  |  |  |  |  |

|                |                                           | Z            | Zero                                                                                  |  |  |  |  |  |  |

|                |                                           | ZF           | Zero flag                                                                             |  |  |  |  |  |  |

Table 3. Instruction Set Summary

| Mnemonic    | Execution        | Byte/  | FI       | ag/St    | atus     | A                                                         |  |  |  |  |  |  |

|-------------|------------------|--------|----------|----------|----------|-----------------------------------------------------------|--|--|--|--|--|--|

| Operand     | Code<br>(in Hex) | Cycle  | ZF       | CF       | ST       | Operation                                                 |  |  |  |  |  |  |

|             | Register Tri     | inster |          |          |          |                                                           |  |  |  |  |  |  |

| TATH        | 05               | 1/1    |          | •        | •        | TH←(AC)                                                   |  |  |  |  |  |  |

| TATL        | 06               | 1/1    | ١.       |          | .        | TL+(AC)                                                   |  |  |  |  |  |  |

| TAY         | 04               | 1/1    |          | .        | .        | Y←(AC)                                                    |  |  |  |  |  |  |

| TTHA        | 15               | 1/1    | 1        | ·        | ·        | AC+-(TH)                                                  |  |  |  |  |  |  |

| TTLA        | 16               | 1/1    | ΙÌ       |          | 1 . 1    | AC←(TL)                                                   |  |  |  |  |  |  |

| TYA         | 14               | 1/1    | ΙÌ       | ١.       |          | AC+-(Y)                                                   |  |  |  |  |  |  |

| XX          | 18               | 1/1    | Ť¹       | ·        | · •      | (AC) <del>↓</del> (X)                                     |  |  |  |  |  |  |

| Register-to | -Memory Tre      | nsfer  |          |          |          |                                                           |  |  |  |  |  |  |

| L           | 0D               | 1/1    | ‡        | ·        | •        | AC{M(X,Y)}                                                |  |  |  |  |  |  |

| ST          | 1D               | 1/1    |          | 1        | •        | M (X,Y) ←(AC)                                             |  |  |  |  |  |  |

| STDC        | 1A               | 1/1    |          | .        | ↓c       | $M(X,Y) \leftarrow (AC), Y \leftarrow (Y)-1$              |  |  |  |  |  |  |

| STIC        | 0A               | 1/1    |          |          | †c       | $M(X,Y) \leftarrow (AC), Y \leftarrow (Y)+1$              |  |  |  |  |  |  |

| ×           | 0B               | 1/1    | 11       |          |          | (AC) = { M(X, Y)}                                         |  |  |  |  |  |  |

| XD D        | 50-53            | 1/1    | 11 1 N   |          | .        | $(AC) \leftarrow \{M(0, D)\}$ ; D = 0 to 3 (X = 0, Y = D) |  |  |  |  |  |  |

| XYD D       | 54-57            | 1/1    | ‡2       | •        | .        | $(Y) \leftarrow \{M(0, D)\}$ ; D = 4 to 7 (X = 0, Y = D)  |  |  |  |  |  |  |

| Constant Tr | ansier           |        |          |          |          |                                                           |  |  |  |  |  |  |

| CLA         | 90               | 1/1    | 1        |          | •        | AC← 0 (Included in LI Instruction)                        |  |  |  |  |  |  |

| LI imm      | 90-9F            | 1/1    | ‡        | •        | •        | AC-imm; imm=0 to 15                                       |  |  |  |  |  |  |

| LXI imm     | 58-5F            | 1/1    | İ        | •        |          | X3←0, X2 to X0←imm; imm=0 to 7                            |  |  |  |  |  |  |

| LXID imm    | 3D90-3D9F        | 2/2    | ‡        | •        |          | X+-imm; imm = 0 to 15                                     |  |  |  |  |  |  |

| LRXA imm    | 3D20-3D3F        | 2/3    |          | .        |          | $X \leftarrow \{ROM ([lmm]X]Y]\} d d = 7-4$               |  |  |  |  |  |  |

|             |                  |        |          | i I      |          | AC-(ROM( Imm X Y )) d, d = 7-4                            |  |  |  |  |  |  |

| LYI imm     | 80-8F            |        |          |          |          | imm = 0 to 154                                            |  |  |  |  |  |  |

|             |                  | 1/1    | <u> </u> | •        | •        | Y←imm; Imm = 0 to 15                                      |  |  |  |  |  |  |

| ADC I       | Logical Op<br>0E |        | •        |          |          |                                                           |  |  |  |  |  |  |

| -           | 3D80-3D8F        | 1/1    | ‡        | ‡        | †c       | AC+-(AC) +{ M(X,Y)} + (CF)                                |  |  |  |  |  |  |

|             |                  | 2/2    | ‡        | ‡        | †c       | AC←(AC) + Imm; Imm=0 to 15                                |  |  |  |  |  |  |

| AND         | 0F               | 1/1    | <b>‡</b> | $\cdot$  | ↓z       | $AC \leftarrow (AC) \cap \{M(X, Y)\}$                     |  |  |  |  |  |  |

| C           | 2E               | 1/1    | ‡        | ‡        | ↓z I     | $\{M(X, Y)\}$ - $(AC)$                                    |  |  |  |  |  |  |

| CI Imm      | B0-BF            | 1/1    | ‡        | ‡        | ↓z<br>↓z | imm- (AC); imm = 0 to 15                                  |  |  |  |  |  |  |

| CYI Imm     | A0-AF            | 1/1    | ٠        | ·        | ↓z       | imm- (Y); imm = 0 to 15                                   |  |  |  |  |  |  |

| DAA         | 10               | 1/1    | ‡        |          | †c       | AC← (AC) +8 If (AC)>9 or (CF) = 1                         |  |  |  |  |  |  |

| DAS         | 11               | 1/1    | ‡        | .        | ic       | AC←(AC) +10 if (AC) >9 or (CF) = 1                        |  |  |  |  |  |  |

| DCA         | 3D8F             | 2/2    | ‡        | ‡        | Įc       | AC←(AC) + 15 (Included in Al instruction)                 |  |  |  |  |  |  |

| DCM         | 19               | 1/1    | İ        |          | ļc       | $M(X, Y) \leftarrow \{M(X, Y)\} -1$                       |  |  |  |  |  |  |

| DCY         | 18               | 1/1    | :        | <u> </u> | ‡c       | Y←(Y)-1                                                   |  |  |  |  |  |  |

| EOR         | 2F               | 1/1    | ‡        |          | ŢΖ       | $AC \leftarrow \{M(X, Y)\} \oplus (AC)$                   |  |  |  |  |  |  |

| ICA         | 3D81             | 2/2    | ‡        | ‡        | ĮС       | AC←(AC) +1 (Included in Al instruction)                   |  |  |  |  |  |  |

| ICM         | 09               | 1/1    | Ť.       |          | ic l     | M(X,Y) ← (M(X,Y) )+1                                      |  |  |  |  |  |  |

| ICX         | 3DAC             | 2/2    |          | ٠ ا      | ţc       | X← (X) +1                                                 |  |  |  |  |  |  |

|             | 08 I             | 1/1    | ‡ l      |          | ĭcl      | · ·                                                       |  |  |  |  |  |  |

| ICY         | V6               |        | +        |          | 1 ⊂ I    | Y← (Y) +1                                                 |  |  |  |  |  |  |

Table 3. Instruction Set Summary (Cont'd)

| Mnemonic   | Execution        |                | Flag/Status |          |            |                                                                                 |

|------------|------------------|----------------|-------------|----------|------------|---------------------------------------------------------------------------------|

| Operand    | Code<br>(in Hex) | Byte/<br>Cycle | ZF          | CF       | ST         | Operation                                                                       |

|            | & Logical O      | peration       |             |          |            |                                                                                 |

| OR         | 1F               | 1/1            | 1           |          | Ιz         | AO{M(X, Y)}∪ (AC)                                                               |

|            |                  |                | $\vdash$    |          | <u> </u>   |                                                                                 |

| ROL        | 0C               | 1/1            | ‡           | ‡        | tc         | CF (A, C, )                                                                     |

| ROR        | 1C               | 1/1            | ‡           | ‡        | ţc         |                                                                                 |

| SBC        | 1E               | 1/1            | ‡           | #        | tc         | AC-{M(X, Y)} - (AC)-(CF)                                                        |

| Bit Manipu | lation           |                |             |          |            |                                                                                 |

| RBIT bp    | 34-37            | 1/1            | ·           | •        | ·          | $\{M(X, Y)\}\ bp \leftarrow 0; bp = 0 to 3$                                     |

| SBIT bp    | 30-33            | 1/1            |             | •        | •          | { M(X, Y) } bp← 1;bp = 0 to 3                                                   |

| RBA bp     | 3DA4-3DA7        | 2/2            |             | •        |            | (AC) bp-0; bp = 0 to 3                                                          |

| SBA bp     | 3DA0-3DA3        | 2/2            |             |          | •          | (AC)bp <sub>←</sub> 1 ; bp = 0 to 3                                             |

| TBA bp     | 4C-4F            | 1/1            |             | ·        | ΙZ         | (AC)bp-1 ; bp = 0 to 3                                                          |

| TBIT bp    | 38-3B            | 1/1            | ١.          | ١.       | ↓z         | $\{M(X, Y)\}$ bp-1; bp = 0 to 3                                                 |

| Control    |                  |                |             |          |            |                                                                                 |

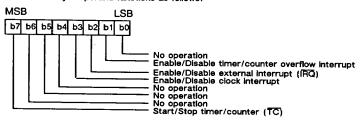

| EN Imm     | 3E00-3EFF        | 2/2 3          |             | ·        | •          | Enable the internal resources by the operand byte (2nd byte) 3                  |

| DIS imm    | 3F00-3FFF        | 2/2 3          | Ŀ           | Ŀ        | · '        | Disable the internal resources by the operand byte (2nd byte) <sup>3</sup>      |

| RST        | 3DAD             | 2/2            | ŀ           | Ŀ        | Ŀ          | System initialization                                                           |

| Input/Outp |                  | , , . ,        |             |          |            |                                                                                 |

| IN<br>INK  | 13<br>12         | 1/1            |             | :        | :          | AC← (R)Y : Y=0 to 3 (Port #)<br>AC← (REG)Y: Y=5, 6, 8, 9, B, C, E, F<br>AC← (K) |

| OUT        | 03               | 1/1            | •           |          | •          | (R)Y← (AC); Y=0 to 3 (Port #)                                                   |

| OUTP       | 02               | 1/1            | ١.          | ١.       | ١.         | (REG)Y← (R); Y=5, 6, 7, 8, 9, B, D<br>P← (AC)                                   |

| OUTX       | 3DAB             | 2/2            | ١.          | ١.       | ١.         | (SEG) Y← AC; Y=0 to 9 (MB88562 only)                                            |

| RSTD d     | 44-47            | 1/1            | ╁╌          | +-       | +          | (R)d←0; d=0 to 3 (Bit # of Port #0)                                             |

| RSTR       | 22               | 1/1            | ١.          | ١.       | ١.         | (R)Y←0; Y=0 to 10 (Bit #)                                                       |

| SETD d     | 40-43            | 1/1            | ١.          | ١.       | ١.         | (R)d <sub>4</sub> -1; d=0 to 3 (Bit # of Port #0)                               |

| SETR       | 20               | 1/1            | ١.          |          | ١.         | (R)Y←1; Y=0 to 10 (Bit #)                                                       |

| TSTD d     | 48-4B            | 1/1            | ١.          | ١.       | ΙZ         | (R)d-1; d=8 to 10 (Bit #)                                                       |

| TSTR       | 24               | 1/1            |             | .        | 1z         | (R)Y-1; Y=0 to 10 (Bit #)                                                       |

| Branch     | 1                | 1              |             | <u> </u> |            | I.                                                                              |

| CALL addr  | 6000-6FFF        | 2/2            | T •         | <u> </u> | •          | If ST=1, Subroutine Call for addr; addr=0 to 4095 4<br>ST=0, No Subroutine Call |

| JMP addr   | C0-FF            | 1/1            | ·           | 1.       | <b>「</b> ・ | If ST=1, Branch to addr, addr=0 to 63; ST=0, No Branch                          |

| JPXY addr  | 3D00-3D1F        | 2/2            | 1.          | 1.       | .          | Branch always to addr on page #n;                                               |

| JPL addr   | 7000-7FFF        | 2/2            | ١.          | 1.       | ١.         | if ST=1, Branch to addr, addr=0 to 4095 4; ST=0, No Branch                      |

| RTI        | 3C               | 1/1            | ┪.          | ╽.       | ╽.         | Return From Interrupt Routine                                                   |

| 1          | I                |                |             | 1        | 1          |                                                                                 |

| RTS        | 2C               | 1/1            | 1.          | 1.       | Ι.         | Return From Subroutine                                                          |

| Table 3. | Instruction | Set | Summan | , ( | (Cont'd) | , |

|----------|-------------|-----|--------|-----|----------|---|

|          |             |     |        |     |          |   |

| Mnemonic   | Execution        | Byte/          | Flag                  | j/Sta | itus | 0                        |

|------------|------------------|----------------|-----------------------|-------|------|--------------------------|

| Operand    | Code<br>(in Hex) | Byte/<br>Cycle | ZF                    | CF    | ST   | Operation                |

| Flag Manip | ulation          |                |                       |       |      |                          |

| RSTC       | 23               | 1/1            | . 1                   | 1     | • 1  | CF← 0                    |

| SETC       | 21               | 1/1            | .                     | ↑     | .    | CF← 1                    |

| тѕтс       | 28               | 1/1            | $\lceil \cdot \rceil$ |       | ↓CF  | (CF) -1                  |

| TSTI       | 25               | 1/1            | ۱. ا                  |       | ŢIF  | (IF)-1, (If IRQ=L, IF=1) |

| TSTV       | 26               | 1/1            | .                     |       | Į∨F  | (VF)-1, VF←0             |

| TSTZ       | 29               | 1/1            | •                     |       | ↓ZF  | (ZF)-1                   |

| Other      |                  |                |                       |       |      |                          |